DAC Picardian chord v1.0

(или как правильно приготовить Дельта Сигму)

Данное устройство построено с использованием оригинальных схемотехнических решений на основании немалого опыта (отсутсвие электролитических конденсаторов даже в питании, развязка источник-усилитель по земле, линейная аналоговая часть итд) и обладает следующими свойствами:

- Прекрасное качество звука

- Правильный S/PDIF вход

- Поддержка форматов DVD-Audio (24бита 96,192кГц), CDDA (16бит 44,1кГц) и других

- Доступность

- Компактность

ЦАП Picardian chord v1.0

Целью создания данного цапа было сделать устройство:

- с очень хорошим качеством звука

- универсальное

- доступное

Доступность подразумевает использование комплектующих выпускаемых на сегодняшний день, универсальность поддержку всех современных форматов ИКМ вплоть до 24бит 192кГц и использование стандартного интерфейса S/PDIF или AES/EBU.

Стандартные S/PDIF приемники с прямым выделением тактовой частоты с помощью ФАПЧ имеют довольно большой уровень джиттера встроенных ГУН и главное совсем не эффективное подавление джиттера в самом главном для нас звуковом диапазоне частот из за очень высокого среза ФНЧ петли ФАПЧ (более 10кгц). Поэтому с разными транспортами и разными соединительными кабелями звучание одного и того же устройства будет очень сильно варьироваться. Одним из решений данной проблемы есть использования асинхронного преобразователя частоты дискретизации(ASRC) после S/PDIF приемника, это позволяет нивелировать входной джиттер но сильно ухудшает качество звука из за наличия лишнего ЦФ не лучшего качества. Правильным выходом из данной ситуации есть использование S/PDIF приемника с низкой частотой среза петли ФАПЧ. В данном устройстве используется S/PDIF приемник с непрямым выделением тактовой частоты WM8804 фирмы Wolfson Microelectronics. [6][7]

Блок схема данного приемника изображена на рис. 1, состоящая из ЦФАПЧ(DPLL), ФИФО буфера (Elastic buffer), аналоговой ФАПЧ(PLL) и ЦФ (IIR).

ЦФАПЧ тактируемая 94,3104Мгц или 98,304Мгц (для ЧД кратных 44,1 или 48кгц) восстанавливает входные данные и такт которые сохраняются в ФИФО буфере, абсорбирующем ВЧ джиттер и используемом также для выявления разницы частот между входным и выходным тактом. Сигнал переполнения или опустошения буфера впоследствии фильтруется цифровым фильтром и является управляющим для ФАПЧ (засинхронизированной на кварцевый ТГ) изменяющим коефициент деления ее петли.

Такое построение S/PDIF приемника позволяет забыть о проблеме джиттера, с любыми источниками данных и соединительными проводами звук будет одинаковый (откровенно кривым транспортам правда ниче не поможет).

В качестве ЦАПа используется гибридный ЦАП фирмы Texas Instruments PCM1794A, выбор именно этого цапа обусловлен его архитектурой, хорошим ЦФ с режимом плавного спада АЧХ что необходимо для раскрытия потенциала записей с высокой частотой дискретизации (96, 192кГц) и который отсутствует у конкурентов в лице AD1955, AD1853, SM5847+SM5865.

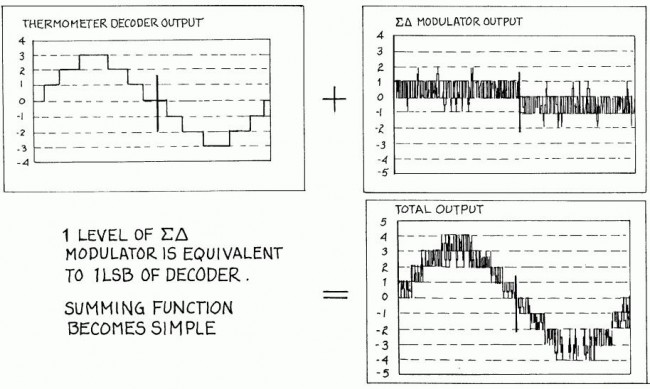

Архитектура данного ЦАП [8][9] изображена на рис. 2, старшие 6 бит входных 24 разрядных данных после 8х ЦФ поступают на Segment decoder (подвид полнодекодированнго цап (fully-decoded/directly-decoded dac) или термометр (thermometer dac) ), а младшие 18 бит (+СЗР) на 5 уровневый SDM 3го порядка[10]. Впоследствии результат суммируется (рис. 3) и подается на разновидность схемы динамической подстройки элементов (DEM) для минимизации влияния неодинаковости ГСТ в цап и разнице в опорных уровнях полнодекодированного цап и SDM.

рис. 3 (пример, реально 67уровней)

рис. 3 (пример, реально 67уровней)

Выход ЦАП токовый дифференциальный (рис. 4) , нуждается во внешнем каскаде Т/Н (I/U) и ФНЧ. Теоретически достижимый ДД такого гибрида покрывает требования 24разрядного звука.

Схема данного устройства изображена на рис. 5

Входные бифазные данные S/PDIF с частотами дискретизации до 192кГц декодируются микросхемой WM8804 и по шине IIS передаются на цифро-аналоговый преобразователь PCM1794A. С помощью переключателей DF и DEM возможно переключение плавности спада ЦФ и включения деемфазиса. Преобразователь ток/напряжение (I/U) и первая ступень ФНЧ сделана на основе дифампов THS4131. C50,C54,C56,C62,C65,C67 обеспечивают низкое входное сопротивление Т/Н на вч и не допускают перегрузки дифампов вч глитчем от работы токового ЦАП PCM1794A соответственно обеспечивая динамическую линейность системы ЦАП->Т/Н в целом. Резисторы R46,R55,R69,R76 компенсируют смещение на входах Т/Н (I/U).

Выходные противофазные сигналы поступают на дифусилитель с второй ступенью ФНЧ на NE5534P формирующий из противофазных сигналов один и обеспечивающий отвязку ЦАП от усилителя по земле, так как выходной сигнал берется не между выходом IC4, IC6 и землей устройства, а между выходом IC4, IC6 и верхнем по схеме выводом R59, R79 , земли устройств при этом напрямую не связаны что позволяет исключить земляные петли и увеличить магнитное экранирование межблочного коаксиального кабеля на 40дб. Но такое включение не обеспечивает работы на нагрузку ниже 4,7кОм поэтому возможно соединение верхних по схеме выводов R59, R79 на землю. R51,R52,R72,R73,C55,C66 фильтруют ВЧ помехи наводимые на соединительные кабеля.

Питание организовано по принципу «каждому потребителю свое» с применением широко известных стабилизаторов LM317/337, имеющих малый шум (<40мкв), хорошее подавление пульсаций и большую мощность. На вводе питания аналоговой части устройства, перед стабилизаторами стоят ФНЧ 10ом –100мкф с частотой среза в 150Гц фильтрующие помехи наводящиеся на кабель подключения питания, и от работы БП с фильтром емкостного типа. Первичные стабилизаторы не используются, так как это лишено любого смысла. В цифровом питании вместо электролитических конденсаторов используются керамические X5R (имеющие меньший ESR, ESL) шунтируемые NP0. Питание аналоговой части устройства организовано по принципу «двойное моно», электролитические конденсаторы не используются, вместо них используются безОООСные электронные заменители имеющие стабильное сопротивление ~0.2Ома в полосе до нескольких десятков мегагерц шунтируемые NP0 0,1мкф Murata GRM31 в непосредственной близости с микросхемами. Такое построение обеспечивает в сравнении с самыми именитыми сериями электролитических конденсаторов заметно лучший результат а также простоту, доступность и небольшую цену.

Резисторы R42,R57,R62,R77 рекомендовано использовать угольные композитные Riken Ohm, Ohmite Little Demon, Ohmite Little Rebel итд либо танталовые. Угольные обязательно должны пройти ЭТТ. Резисторы R43,R44,R51,R52,R58,R59,R63,R64,R72,R73,R78,R79 угольные MELF (например KOA RD41). В качестве IC3,IC5 возможно использование THS4131, OPA1632, THS4141 , THS4151, в качестве IC4,IC6 NE5534, LME49710, LME49870, LM318, LT1468, LM6171. Резисторы R46,R55;R69,R76; R42,R57;R62,R77; R43,R58; R44,R59; R63,R78; R64,R79; нужно подобрать попарно с точностью не менее 0,1%.

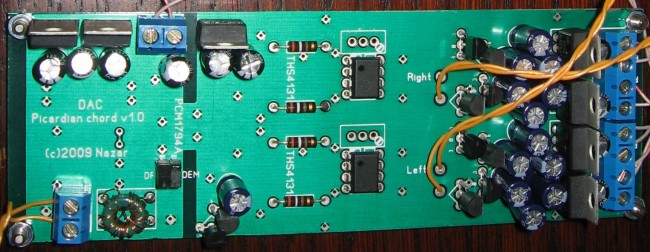

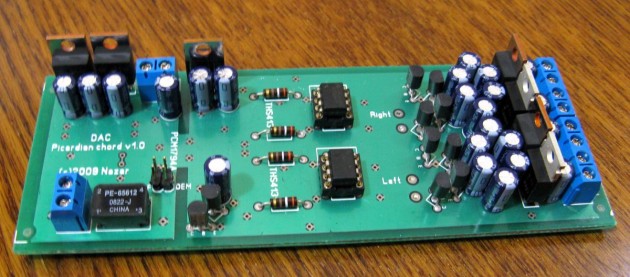

На рис. 6 изображен список деталей и их количество использованых в даном устройстве, а на рис. 7 фото ЦАП Picardian chord v1.0 (печатная плата размером 150х50мм).

Литература:

- “Jitter: Specification and assessment in digital audio equipment” Julian Dunn

- “The diagnosis and solutions of jitter related problems in digital audio systems” Julian Dunn and Lan Dennis

- “TOWARDS COMMON SPECIFICATIONS FOR DIGITAL AUDIO INTERFACE JITTER” Julian Dunn, Barry A.

McKibben, Roger Taylor, Chris Travis - “Is the AES/EBU/SPDIF Digital Audio Interface flawed?”, C Dunn and M Hawksford, AES 93rd Convention San Francisco, preprint 3360, October 1992

- “Specifying the Jitter Performance of Audio Components”, C. Travis and P. Lesso, AES 117 th Convention, October 2004

- “A high performance S/PDIF receiver”, Paul Lesso , AES 121th Convention, San Francisco, October 2006

- “Clock synchroniser and clock and data recovery apparatus and method”, Paul Lesso , US patent

US2005/0220240 A1 - “A 126dB DR Current-mode Advanced Segmented DAC” Norio Terada & Shige Nakao, Texas Instruments Japan, Kanagawa, Japan. AES Paper no. uk076, March 2001.

- “Digital to analog converting method and digital to analog converter employing common weight generating elements” Shigetoshi Nakao, Toshihiko Hamasaki , US patent US 6,469,648 B2

- “A 3-V, 22-mW Multibit Current-Mode SD DAC with 100 dB Dynamic Range” Toshihiko Hamasaki, Yoshiaki Shinohara, Hitoshi Terasawa, Kou-Ichirou Ochiai, Masaya Hiraoka, and Hideki Kanayama. IEEE JOURNAL OF SOLID-STATE CIRCUITS, VOL. 31, NO. 12, DECEMBER 1996

- И.Достал “Операционные усилители” Москва “Мир” 1982р.

- “A Wide-Band, Low-Power, High Slew Rate Voltage-Feedback Operational Amplifer” Farhood Moraveji. IEEE JOURNAL OF SOLID–STATE CIRCUITS, VOL. 31, NO. 1, JANUARY 1996

Спасибо всем тем кто так или иначе поддерживает и помогает мне в этом нелегком деле

качественного звука, отдельно хочу поблагодарить С.И.Агеева за редкие но меткие консультации.

(с)2009г. Львов, Штыбель Назар aka Nazar.

Удачи всем и удовольствия от прослушивания любимых записей!

PS Не для повторения, в схеме имеются ошибки.

27.04.2009

"Directly or indirectly, all questions connected with this subject must come for decision to the ear, as the organ of hearing; and from it there can be no appeal" J.W.S. Rayleigh